Статическая оперативная память

Статическая память (SRAM) – это энергозависимая полупроводниковая память с произвольным доступом, в которой каждый разряд хранится в триггере, позволяющем поддерживать состояние разряда без постоянной перезаписи. Для организации чтения и записи из ячейки памяти дополнительно используется три или более транзисторов.

Содержание.

1. Устройство триггера.

Для того чтобы понять принцип работы статической памяти, обратимся к истокам схемотехники. И начнем с описания принципа работы триггера, изображенного на рисунке 1.

Триггер – это элемент памяти с двумя стабильными состояниями – «0» и «1». В установленном состоянии триггер сохраняется, пока на него подается питание.

Обычно триггер имеет два входа:

и два выхода: Q и инвертированное Q (

Входы R и S используются для установки состояния триггера. Если на вход S подать напряжение, соответствующее логической единице (далее просто логическую единицу), а на вход R – напряжение, соответствующее логическому нулю (далее просто логический ноль), то триггер перейдет в состояние единицы и сохранит это состояние даже, если на вход S перестать подавать сигнал.

Если на вход S подать логический ноль, а на вход R – логическую единицу, то триггер перейдет в состоянии сохранения нуля.

При подаче на оба входа логического нуля, состояние триггера не измениться.

При подаче на оба входа логической единицы, в общем случае состояние триггера будет неопределенно, то есть неизвестно, в какое состояние он перейдет.

На выходах Q и

В таблице 1 приводится перечень всех возможных состояний триггера.

| S | R | Qi | Qi+1 |  i i |  i+1 i+1 |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | ? | 1 | ? |

| 1 | 1 | 1 | ? | 0 | ? |

Таблица 1. Состояния триггера, в зависимости от сигналов на входе.

Рассмотрев логику работы триггера, давайте разберемся, как же он устроен. Структурная схема триггера приведена на рисунке 2.

Как видно из рисунка, состоит он из двух инвертеров (логических элементов «НЕ»), причем выход одного инвертера замкнут на вход другого.

Давайте рассмотрим, как же работают эти инвертеры при подаче различных сигналов на вход.

Первый случай, на вход S подана логическая единица, а на вход R – логический ноль, то есть установка триггера в единичное состояние. И так, если на вход S подать логическую единицу, то, пройдя через инвертер D.D2, она примет значение логического нуля. Таким образом, на выходе

Если сигналы с входов снять (на вход S и R подать логический ноль), то состояние триггера не изменится. Логическая единица с выхода инвертера D.D1 пойдет на вход инвертера D.D2, а логический ноль с выхода D.D2 пойдет на вход инвертера D.D1, в результате чего на выходе инвертера D.D1 будет логическая единица. То есть мы замкнули цикл, который будет продолжаться до тех пор, пока будет на триггер подводиться питание. Зачем нужно питание, рассмотрим чуть позже, когда будем разбирать принцип устройства инвертера.

Рассмотрим второй случай, когда на вход S подан логический ноль, а на вход R –логическая единица, то есть сброс триггера. И так, если на вход S подать логический ноль, то, пройдя через инвертер D.D2, он примет значение логической единицы. Таким образом, на выходе

Так же, как и в первом случае, при снятии сигналов с входов R и S состояние триггера не изменится.

Давайте теперь более подробно рассмотрим принцип работы инвертера. Существуют различные способы организации инвертера, мы рассмотрим только один из них, самый простой. Этого будет вполне достаточно, чтобы понять принцип его организации. И так на рисунке 4 изображена структурная схема инвертера.

На рисунке представлена простейшая схема реализации инвертера, состоящая из одного транзистора. Давайте рассмотрим, как он работает.

На элемент всегда подается питание Uп. В результате, создаваемый ток может пойти либо по линии AB, в этом случае на выходе инвертера ток будет отсутствовать (будет логический ноль), либо – по линии AC, в этом случае на выходе инвертера ток будет присутствовать (будет логическая единица).

По линии AB ток пойдет, если транзистор VT1 будет открыт, а для этого необходимо подать напряжение на вход инвертера.

По линии AC ток пойдет, если транзистор VT1 будет закрыт, а это произойдет при отсутствии напряжении на входе инвертера.

Таким образом, если на вход инвертера подается логическая единица, то на выходе будет логический ноль. И, соответственно, при подаче на вход инвертера логического нуля, на выходе будет поучена логическая единица.

2. Устройство ячейки статической памяти.

Теперь, зная, как работает триггер и инвертер, рассмотрим устройство ячейки статической памяти и принцип ее работы. Естественно, рассматривать мы будем простейшую ячейку памяти. На практике используют множество дополнительных ухищрений для повышения скорости работы статической памяти. Но, зная принцип работы элементарной ячейки статической памяти, вы без особого труда в дальнейшем разберетесь и в принципе работы других реализаций ячеек статической памяти.

На рисунке 4 приведена упрощенная схема одного из способов организации ячейки статической памяти.

Как видите, она состоит из одного триггера и трех транзисторов, выполняющих роль ключей, открывающих и закрывающих доступ к ячейке памяти. Транзисторы VT1 и VT2 используются для разрешения и запрета записи в ячейку, а транзистор VT3 – для разрешения и запрета чтения.

Для записи данных необходимо подать напряжение в линию строки, после чего транзисторы VT1, VT2 и VT3 откроются. Затем для записи единицы необходимо подать напряжение, соответствующее логической единице, на линию D и напряжение, соответствующее логическому нулю, на линию

В установленном состоянии триггер будет оставаться даже после снятия напряжения с линии строки и с линий D и

Для считывания данных необходимо на выходы D и

Считывание данных с ячейки статической памяти, в отличие от чтения с ячейки динамической памяти, не приводит к потере сохраненного бита данных, поэтому, перезапись данных в ячейку статической памяти не требуется.

3. Устройство микросхемы статической памяти.

Давайте перейдем к следующему этапу изучения работы статической памяти и рассмотрим ее общую логику работы. Для этого обратимся к упрощенной структурной схеме статической памяти, изображенной на рисунке 5.

Начнем с записи данных в статическую память и рассмотрим случай записи единицы в ячейку М11.

В контроллер шины памяти от контроллера памяти, встроенного в северный мост материнской платы или в процессор, приходит адрес ячейки памяти и данные для записи. Адрес ячейки преобразуется на две составляющие – номер строки и номер столбца. Номер строки передается в «Дешифратор адреса строки», откуда на нужную строку подается напряжение.

Так как мы рассматриваем запись в ячейку М11, то напряжение с дешифратора адреса строки подается на первую строку. В результате, транзисторы VT1, VT2 и VT3 открываются. Аналогичные транзисторы других ячеек памяти, располагающихся в этой строке, также открываются.

Через транзистор VT3 первой ячейки и аналогичные транзисторы других ячеек памяти первой строки пойдет ток, соответствующий состоянию триггеров этих ячеек, в «Буфер данных». Однако «Буфер данных» получаемую информацию будет игнорировать, так как у него нет сигнала от «Блока управления» на сохранение считываемых данных.

Блоки записи используются для запрета выдачи тока в линии D и

В нашем случае, запись проводится в ячейку М11, и записывается единица. Соответственно, с «Блока работы с данными» будет выдана логическая единица в «Блок записи 1», и с «Блока дешифровки адреса столбца» будет выдана логическая единица в «Блок записи 1».

Рассмотрим работу «Блока записи 1» при таких входных сигналах. И так, на входе элемента D.D3 будет логическая единица, а на выходе – логический ноль, так как элемент D.D3 – инвертер (логический элемент «НЕ»). Соответственно, на входах элемента D.D4 (логический элемент «И») будут: логический ноль и логическая единица. В результате, на выходе этого элемента будет логический ноль.

На входах элемента D.D5 (логический элемент «И») будут две логические единицы, в результате, на выходе этого элемента будет логический ноль.

Следовательно, на выходе D1 «Блока записи 1» будет напряжение, соответствующее логическому нулю, а на выходе

После изменения состояния триггера первой ячейки напряжение с первой строки снимается, и транзисторы VT1, VT2 и VT3 закрываются, запрещая запись и чтение из ячейки.

При записи нуля в ячейку памяти все происходит по той же схеме, только с «Блока работы с данными» в «Блок записи 1» будет подано напряжение, соответствующее логическому нулю. Это значит, что на выходе D1 «Блока записи 1» будет напряжение, соответствующее логической единице, а на выходе

В установленном состоянии триггер первой ячейки останется, пока на него будет подаваться питание Uп.

Чтение записи происходит еще проще. От контроллера памяти приходит адрес ячеек памяти, с которых требуется считать данные, и команда на чтение.

В результате, адрес преобразуется в номер строки, и на соответствующую строку будет подано напряжение, которое откроет транзисторы разрешения/запрета чтения/записи.

Рассмотрим случай, когда данные считываются из первой ячейки. В этом случае напряжение с «Дешифратора адреса строки» будет подано в первую строку, что приведет к открытию транзисторов VT1, VT2 и VT3 ячейки М11 и всех остальных ячеек первой строки. Ток с триггера первой ячейки, через транзистор VT1, беспрепятственно пройдет в «Буфер данных». То же самое произойдет с остальными ячейками первой строки. Считанные с ячеек памяти первой строки данные сохранятся в «Буфере данных».

После того, как информация в «Буфере данных» будет сохранена, «Дешифратор адреса столбцов» выдаст номера столбцов, данные с которых необходимо считать, в «Буфер данных». Соответствующие данные будут переданы из микросхемы памяти в контроллер памяти, располагающийся в материнской плате или непосредственно в процессоре.

Для того чтобы при чтении данных не происходила запись в эти же ячейки, ведь транзисторы, разрешающие запись, открыты, блоки записи выдают в линии D и

Как видите, работа статической памяти очень похожа на работу динамической памяти, однако процесс записи и чтения гораздо быстрее, так как не тратится время на заряд и разряд конденсаторов и не требуется регенерация ячеек. Однако необходимо обратить внимание, что рассмотренная нами схема сильно упрощена, и на практике используют гораздо более сложные механизмы записи и чтения из памяти, повышающие надежность и скорость работы статической памяти. Однако описанный выше принцип работы позволяет понять основы функционирования статической памяти, ее недостатки и преимущества. Давайте попробуем сформулировать их (основные недостатки и преимущества).

4. Достоинства и недостатки статической памяти.

В связи с перечисленными выше достоинствами и недостатками, область применения статической памяти ограничивается, в основном, использованием ее в качестве КЭШ-памяти, что позволяет при небольшом увеличении стоимости уменьшить влияние недостатков динамической памяти на производительность ЭВМ. Однако, это все лишь компромисс, позволяющий несколько сгладить разрыв в производительности процессора и памяти, и все вытекающие отсюда последствия.

Требуется кардинальное решение проблемы существующей с момента зарождения вычислительной техники. Существует множество экспериментальных разработок, позволяющих получить быструю и дешевую оперативную память, но многие из них пока существуют только в виде лабораторных образцов, многие имеют недостаточную надежность и так далее. Наиболее перспективный путь развития оперативной памяти – это использование магниторезистивной памяти, получающей все большее распространение.

SRAM (память)

Статическая оперативная память с произвольным доступом ( SRAM, static random access memory ) — полупроводниковая оперативная память, в которой каждый двоичный или троичный разряд хранится в схеме с положительной обратной связью, позволяющей поддерживать состояние без регенерации, необходимой в динамической памяти (DRAM). Тем не менее, сохранять данные без перезаписи SRAM может только пока есть питание, то есть SRAM остается энергозависимым типом памяти. Произвольный доступ (RAM — random access memory) — возможность выбирать для записи/чтения любой из битов (тритов) (чаще байтов (трайтов), зависит от особенностей конструкции), в отличие от памяти с последовательным доступом (SAM — sequential access memory).

Содержание

Двоичная SRAM

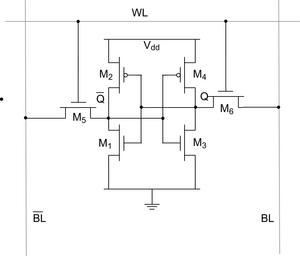

Типичная ячейка статической двоичной памяти (двоичный триггер) на КМОП-технологии состоит из двух перекрёстно (кольцом) включённых инверторов и ключевых транзисторов для обеспечения доступа к ячейке (рис. 1.). Часто для увеличения плотности упаковки элементов на кристалле в качестве нагрузки применяют поликремниевые резисторы. Недостатком такого решения является рост статического энергопотребления.

Линия WL (Word Line) управляет двумя транзисторами доступа. Линии BL и BL (Bit Line) — битовые линии, используются и для записи данных и для чтения данных.

Запись. При подаче «0» на линию BL или BL параллельно включенные транзисторные пары (M5 и M1) и (M6 и M3) образуют логические схемы 2ИЛИ, последующая подача «1» на линию WL открывает транзистор M5 или M6, что приводит к соответствующему переключению триггера.

Чтение. При подаче «1» на линию WL открываются транзисторы M5 и M6, уровни записанные в триггере выставляются на линии BL и BL и попадают на схемы чтения.

Переключение триггеров через транзисторы доступа является неявной логической функцией приоритетного переключения, которая в явном виде, для двоичных триггеров, строится на двухвходовых логических элементах 2ИЛИ-НЕ или 2И-НЕ. Схема ячейки с явным переключением является обычным RS-триггером. При явной схеме переключения линии чтения и записи разделяются, отпадает нужда в транзисторах доступа в схеме записи-чтения с неявным приоритетом(по 2 транзистора на 1 ячейку), но появляется нужда в схемах записи-чтения с явным приоритетом.

В настоящее время появилась усовершенствованная схема [2] с обратной связью отключаемой сигналом записи, которая не требует транзисторов нагрузки и соответственно избавлена от высокого потребления энергии при записи.

Троичная SRAM

Один логический элемент 2ИЛИ-НЕ состоит из двух двухзатворных транзисторов (четырёх однозатворных), три — из шести (двенадцати однозатворных), плюс три транзистора доступа, всего — девять транзисторов (пятнадцать) на одну трёхбитную ячейку памяти (трит).

Преимущества

Недостатки

Тем не менее, высокое энергопотребление не является принципиальной особенностью SRAM, оно обусловлено высокими скоростями обмена с данным видом внутренней памяти процессора. Энергия потребляется только в момент изменения информации в ячейке SRAM.

Применение

SRAM применяется в микроконтроллерах и ПЛИС, в которых объём ОЗУ невелик (единицы килобайт), зато нужны низкое энергопотребление (за счёт отсутствия сложного контроллера динамической памяти), предсказываемое с точностью до такта время работы подпрограмм и отладка прямо на устройстве.

В устройствах с большим объёмом ОЗУ рабочая память выполняется как DRAM. SRAM’ом же делают регистры и кеш-память.

См. также

Примечания

| Это заготовка статьи о компьютерах. Вы можете помочь проекту, исправив и дополнив её. Это примечание по возможности следует заменить более точным. |

Микроконтроллеры Микроконтроллеры | |||||||

|---|---|---|---|---|---|---|---|

| Архитектура |

| ||||||

| Производители | Analog Devices • Atmel • Silabs • Freescale • Fujitsu • Holtek • Hynix • Infineon • Intel • Microchip • Maxim • Parallax • NXP Semiconductors • Renesas • Texas Instruments • Toshiba • Ubicom • Zilog • Cypress | ||||||

| Компоненты | Регистр • Процессор • SRAM • EEPROM • Флеш-память • Кварцевый резонатор • Кварцевый генератор • RC-генератор • Корпус | ||||||

| Периферия | Таймер • АЦП • ЦАП • Компаратор • ШИМ-контроллер • Счётчик • LCD • Датчик температуры • Watchdog Timer | ||||||

| Интерфейсы | CAN • UART • USB • SPI • I²C • Ethernet • 1-Wire | ||||||

| ОС | FreeRTOS • μClinux • BeRTOS • ChibiOS/RT • eCos • RTEMS • Unison • MicroC/OS-II • Nucleus | ||||||

| Программирование | JTAG • C2 • Программатор • Ассемблер • Прерывание • MPLAB • AVR Studio • MCStudio | ||||||

Полезное

Смотреть что такое «SRAM (память)» в других словарях:

SRAM — SRAM: SRAM (память) один из видов компьютерной памяти, статическая память с произвольным доступом. SRAM (компания) американская компания, один из крупнейших в мире производителей оборудования для велосипедов. См. также Срам … Википедия

Память с произвольной выборкой — Варианты конструкции модулей RAM, используемые в качестве ОЗУ компьютеров. Сверху вниз: DIP, SIPP, SIMM 30 pin, SIMM 72 pin, DIMM, DDR DIMM Запоминающее устройство с произвольным доступом ЗУПД (или Запоминающее устройство произвольной выборки… … Википедия

Память с произвольным доступом — Варианты конструкции модулей RAM, используемые в качестве ОЗУ компьютеров. Сверху вниз: DIP, SIPP, SIMM 30 pin, SIMM 72 pin, DIMM, DDR DIMM Запоминающее устройство с произвольным доступом ЗУПД (или Запоминающее устройство произвольной выборки… … Википедия

Память с изменением фазового состояния — Для термина «PCM» см. другие значения. Типы компьютерной памяти Энергозависимая DRAM (в том числе DDR SDRAM) SRAM Перспективные T RAM Z RAM TTRAM Из истории Память на линиях задержки Запоминающая электронстатическая трубка Запоминающая ЭЛТ Эн … Википедия

Память на магнитных сердечниках — Типы компьютерной памяти Энергозависимая DRAM (в том числе DDR SDRAM) SRAM Перспективные T RAM Z RAM TTRAM Из истории Память на линиях задержки Запоминающая электронстатическая трубка Запоминающая ЭЛТ Энергонезависимая ПЗУ … Википедия

Память на линиях задержки — Типы компьютерной памяти Энергозависимая DRAM (в том числе DDR SDRAM) SRAM Перспективные T RAM Z RAM TTRAM Из истории Память на линиях задержки Запоминающая электронстатическая трубка Запоминающая ЭЛТ Энергонезависимая … Википедия

SRAM (static random access memory) — Статическая память (static RAM), применяемая на наиболее критичных к скорости участках процессоров … Глоссарий терминов бытовой и компьютерной техники Samsung

SRAM (static random access memory) — Статическая память (static RAM), применяемая на наиболее критичных к скорости участках процессоров … Глоссарий терминов бытовой и компьютерной техники Samsung

Магниторезистивная оперативная память — Типы компьютерной памяти Энергозависимая DRAM (в том числе DDR SDRAM) SRAM Перспективные T RAM Z RAM TTRAM Из истории Память на линиях задержки Запоминающая электронстатическая трубка Запоминающая ЭЛТ Энергонезависимая … Википедия

Оперативная память — Запрос «ОЗУ» перенаправляется сюда; см. также другие значения. Модули ОЗУ для ПК … Википедия